تقویت کننده JFET سورس مشترک (Common Source JFET Amplifier)

تقویتکنندههای سیگنال کوچک را با «ترانزیستورهای اثر میدان» (Field Effect Transistors) یا FET نیز میتوان ساخت. این قطعات، نسبت به ترانزیستورهای دوقطبی مزایایی مانند امپدانس ورودی بسیار بزرگ و خروجی با نویز کم دارند که آنها را برای استفاده در تقویتکنندههایی با سیگنال ورودی بسیار کوچک، ایدهآل کرده است. در این آموزش، تقویتکننده JFET سورس مشترک را بررسی میکنیم که پرکاربردترین مدار تقویتکننده JFET است.

اصول طراحی مدار تقویتکننده بر اساس ترانزیستور پیوندی اثر میدان یا «JFET» (در اینجا، FET کانال N) یا حتی ترانزیستور اثر میدان اکسید سیلیسیم فلزی (Metal Oxide Silicon FET) یا MOSFET دقیقاً مشابه مدار ترانزیستوری تقویتکننده کلاس A است

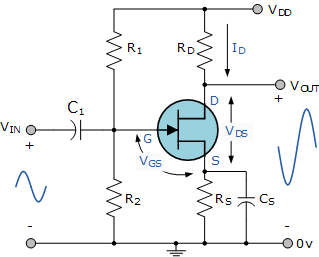

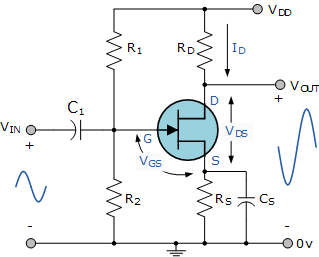

ابتدا باید یک نقطه ساکن یا «Q-Point» مناسب را برای بایاس صحیح تقویتکننده JFET با پیکربندیهای «سورس مشترک» (Common Source) یا CS، «درین مشترک» (Common Drain) یا CD یا «سورس پیرو» یا سورس فالوئر (Source Follower) یا SF و «گیت مشترک» (Common Gate) یا CG پیدا کنیم. این سه پیکربندی، متناظر با پیکربندیهای امیتر مشترک، امیتر پیرو یا امیتر فالوئر (Source Follower) و بیس مشترک ترانزیستورهای دوقطبی هستند. مدار تقویتکننده سورس مشترک در شکل زیر نشان داده شده است:

تقویتکننده JFET سورس مشترک

مدار تقویتکننده از یک JFET کانال N تشکیل شده که میتوان به جای آن، یک ماسفت مُد تخلیه (Depletion-Mode) با تغییر در FET به کار برد. ولتاژ گیت FET یا Vg با یک شبکه مقسم ولتاژ بایاس میشود که از مقاومتهای R1 و R2 تشکیل شده است. این بایاس برای کار در ناحیه اشباع است که معادل با ناحیه فعال ترانزیستور پیوندی دوقطبی محسوب میشود.

برخلاف مدار ترانزیستوری دوقطبی، جریان ورودی گیت JFET تقریباً صفر است و به این ترتیب، گیت به صورت مدار باز عمل میکند. بنابراین، به منحنیهای مشخصه ورودی نیازی نیست. جدول زیر مقایسه JFET با BJT را نشان میدهد:

| JFET | BJT |

| گیت (G) | بیس (B) |

| درین (D) | کلکتور (C) |

| سورس (S) | امیتر (E) |

| ولتاژ گیت (VG) | ولتاژ بیس (VB) |

| ولتاژ درین (VDD) | ولتاژ کلکتور (VCC) |

| جریان درین (ID) | جریان کلکتور (IC) |

از آنجایی که JFET کانال N، یک قطعه مد تخلیه و در حالت نرمال روشن یا وصل (ON) است، باید ولتاژ گیت نسبت به سورس منفی باشد تا جریان درین را مدوله یا کنترل کند. این ولتاژ منفی را میتوان با بایاس از ولتاژ منبع تغذیه مستقل تامین کرد. همچنین میتوان با یک فرایند خود بایاس کننده تا زمانی که یک جریان ماندگار در JFET برقرار است (حتی با عدم وجود سیگنال ورودی) ولتاژ گیت-سورس را مهیا کرد.

در اینجا از یک مقسم ولتاژ استفاده میکنیم که موجب میشود سیگنال ورودی در گیت، افت ولتاژ ایجاد کند. هر ترکیب مناسبی از دو مقاومت، بایاس ولتاژ صحیحی ایجاد خواهد کرد. ولتاژ DC بایاس گیت (Vg) به صورت زیر محاسبه میشود:

توجه کنید که این معادله، تنها نسبت مقاومتهای R1 و R2 را تعیین میکند و به دلیل امپدانس بسیار زیاد ورودی JFET و کاهش اتلاف توان مدار، باید مقادیر این مقاومتها را تا حد امکان بزرگ (1MΩ تا 10MΩ) انتخاب کنیم.

ورودی (Vin) تقویتکننده JFET سورس مشترک، بین پایه گیت و زمین (0V) قرار میگیرد. با اعمال ولتاژ Vg ثابت گیت، JFET مانند یک مقاومت خطی در «ناحیه اهمی» کار میکند. در مدار درین، مقاومت بار Rd وجود دارد که یک سر ولتاژ خروجی Vout به این مقاومت وصل است.

بازده تقویتکننده JFET سورس مشترک را میتوان با افزودن مقاومت Rs افزایش داد که به سورس وصل شده و جریانی برابر جریان درین از آن میگذرد. این مقاومت Rs برای تنظیم نقطه کار تقویتکنندههای JFET نیز به کار میرود.

وقتی JFET بهطور کامل ON است، ولتاژی برابر Rs*Id در مقاومت ایجاد شده و ولتاژ سورس از «0» فراتر خواهد رفت. این افت ولتاژ ناشی از جریان درین در Rs، شرایط بایاس معکوس را برای مقاومت گیت R2 با تولید فیدبک منفی فراهم میکند.

برای نگه داشتن بایاس معکوس پیوند گیت-سورس، ولتاژ سورس Vs باید بزرگتر از ولتاژ گیت Vg باشد. این ولتاژ به صورت زیر است:

![]()

جریان درین Id که برابر با جریان سورس Is نیز هست (چون جریانی به گیت وارد نمیشود)، با رابطه زیر محاسبه میشود:

وقتی بایاس مقسم ولتاژ از یک منبع DC فراهم شود، پایداری مدار تقویتکننده JFET سورس مشترک را نسبت به مدار بایاس ولتاژ ثابت بهبود میدهد. هر دو مقاومت Rs و خازن بایپس Cs، عملکردی مشابه مقاومت و خازن امیتر در مدار تقویتکننده ترانزیستوری امیتر مشترک دارند که پایداری مناسبی ایجاد کرده و از کاهش بهره ولتاژ جلوگیری میکند. البته، هزینه تامین ولتاژ گیت پایدار، بیشتر از ولتاژ تغذیهای است که روی Rs میافتد.

مقدار خازن بایپس سورس معمولاً بیشتر از 100 میکروفاراد است و قطبی میشود. در نتیجه، امپدانس خازن به میزان 10 درصد از هدایت انتقالی (Transconductance) یا gm (ضریب انتقال نشان دهنده بهره) کوچکتر خواهد شد. خازن بایپس، در فرکانسهای بالا اتصال کوتاه میشود و سورس مستقیماً به زمین متصل خواهد شد.

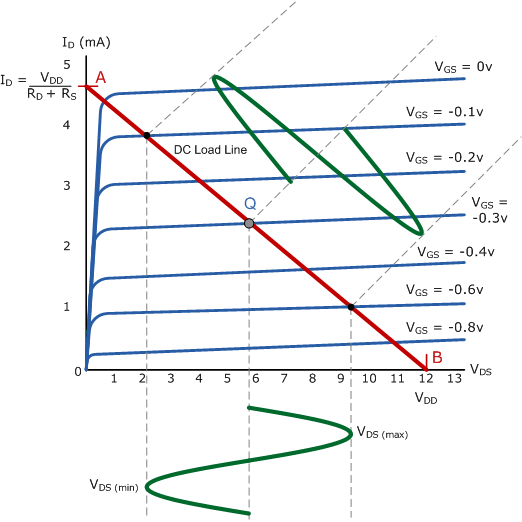

مدار پایه و مشخصه تقویتکننده JFET بسیار شبیه به تقویتکننده امیتر مشترک است. خط بار DC، با اتصال دو نقطه مربوط به جریان درین Id و ولتاژ تغذیه Vdd رسم میشود. لازم به یادآوری است وقتی Id=0 شود، Vdd=Vds است و وقتی Vds=0 شود، Id=Vdd/RL است. بنابراین، خط بار، در نقاط کار با منحنیها برخورد میکند. شکل زیر این موضوع را نشان میدهد.

منحنیهای مشخصه تقویتکننده JFET سورس مشترک

مشابه مدار امیتر مشترک، خط بار DC تقویتکننده سورس مشترک، معادله خط راستی خواهد داشت و شیب آن برابر با −1/(Rd+Rs) است که محور عمودی Id و محور افقی را به ترتیب، در نقطه A برابر (Vdd/(Rd+Rs و نقطه B برابر Vdd قطع میکند. موقعیت نقطه کار معمولاً در وسط خط بار DC قرار دارد و مقدار آن برابر با میانگین Vg است که به دلیل مد تخلیه JFET بایاسِ منفی شده است. خروجی تقویتکننده سورس مشترک، مانند تقویتکننده امیتر مشترک، ۱۸۰ درجه از سیگنال ورودی عقبتر است.

یکی از معایب اصلی استفاده از JFET مد تخلیه، نیاز آن به بایاس منفی است. اگر به هر دلیلی ولتاژ گیت-سورس با افزایش جریان درین، افزایش یافته و بزرگ شود، این بایاس با مشکل مواجه میشود. اگر مقدار مقاومت کانال (Rds(on بالا باشد، با عبور جریان درین از آن، قطعه داغ شده و به هیتسینک بزرگتری نیاز دارد.

ماسفتها امپدانس ورودی بزرگتر و مقاومت کانال کمتری نسبت به JFETهای معادل دارند. بایاس ماسفتها نیز متفاوت است و آنها را برای کانال N به صورت مثبت و برای کانال P منفی بایاس میکنند.

بهره توان و ولتاژ تقویتکننده JFET

قبلاً گفتیم که جریان ورودی Ig تقویتکننده JFET سورس مشترک به دلیل امپدانس ورودی (Rg) بسیار بزرگ، خیلی کم است. بنابراین، نسبت بین امپدانس خروجی و ورودی در این تقویتکننده بسیار مناسب است و برای هر مقدار جریان خروجی IOUT، تقویتکننده، بهره جریان (Ai) بالایی خواهد داشت.

به همین دلیل است که تقویتکنندههای JFET، مدارهای تطبیق امپدانس ارزشمندی هستند و به عنوان تقویتکننده ولتاژ نیز از آنها استفاده میشود. همچنین، از آنجایی که توان برابر ضرب جریان در ولتاژ است، و ولتاژ خروجی در حد چند میلیولت یا حتی ولت است، بهره توان (Ap) نیز بسیار بالاست.

در آموزش بعدی با عنوان «اعوجاج تقویتکننده»، خواهیم دید چگونه بایاس نادرست سبب اعوجاج سیگنال خروجی خواهد شد.